# 系统指令

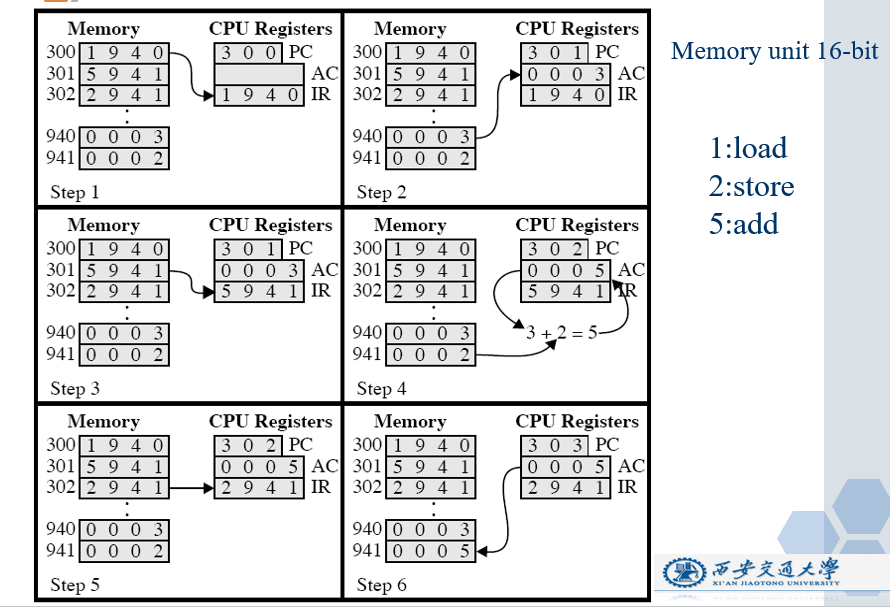

- 计算机的基本功能是执行程序 (指令序列),以完成特殊任务

- CPU 是一个执行指令的部件

- CPU 处理一条指令的时间称为指令周期

- 一条指令的执行可以简单地分为两个步骤:

- 取指令 —— 取周期

- 执行指令 - 执行周期

# 指令周期

# 取指

- 处理器从 PC 指向的内存位置获取指令

- PC 增加

- 除非另有说明

- 指令装入指令寄存器 (IR)

- 处理器解释指令并执行所需的操作

# 执行

- Processor-memory

CPU 和主存之间的数据传输 - 处理器 - I / O

CPU 与 I/O 模块之间的数据传输 - 数据处理

数据上的一些算术或逻辑运算 - 控制

操作顺序的改变

例如 jump - 以上的组合

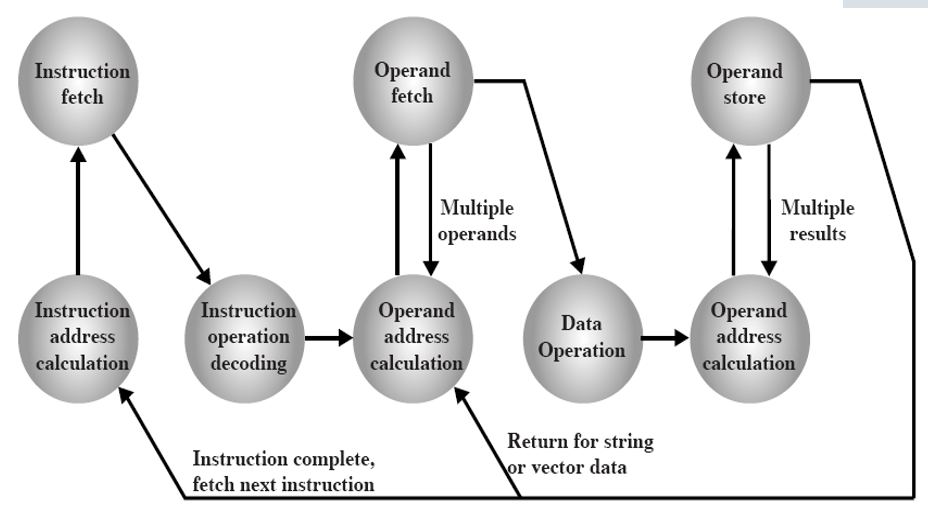

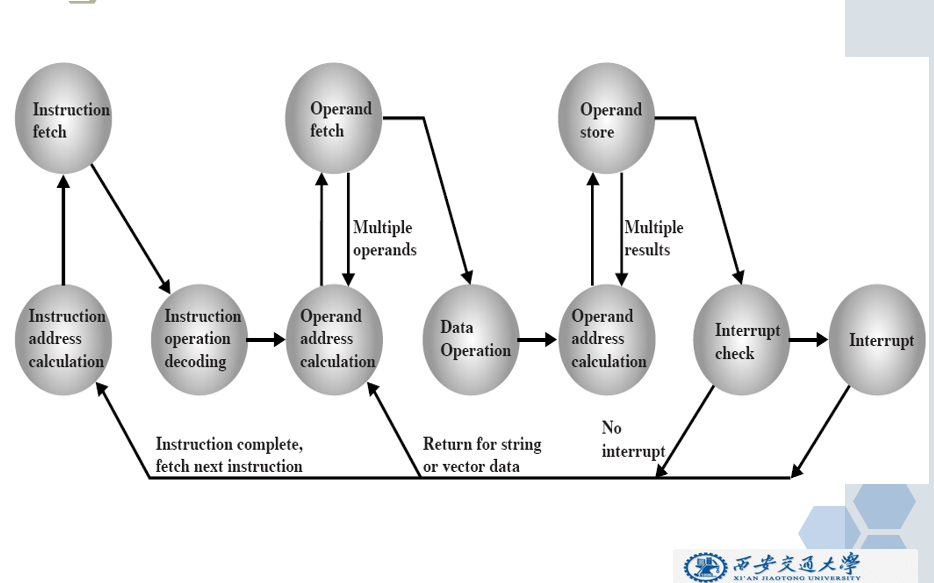

# 指令流程

指令地址计算

指令取出

指令操作解码

操作数地址计算

操作数取

数据操作

操作数的存储

# 中断

- 一种允许其他模块中断 CPU 执行顺序的机制

- 中断的目的

来提高 CPU 的利用率

允许 CPU 处理紧急事件

# 中断的类型

- 程序

例如溢出、除零、非法指令、外部引用 - 计时器

由内部处理器定时器生成

用于先发制人的多任务处理? - I / O

I/O 控制器 - 硬件故障

存储器奇偶校验错误等

# 如果中断挂起,处理器执行以下操作:

暂停正在执行的当前程序的执行,并保存其上下文

Suspend execution of the current program being executed and save its context

保存 PC 的当前上下文和其他数据

Save current context of PC and other data

将 PC 设置为中断处理程序例程的起始地址

Set the PC to starting address of an interrupt handler routine

用户程序不需要包含任何专门的代码来容纳中断

The user program does not have to contain any special code to accommodate interrupts

处理器和操作系统负责暂停和恢复用户程序

The processor and OS are responsible for suspending the user program and resuming it

# 中断周期被加到指令周期中

在一个指令周期之后,处理器检查中断,由中断信号指示

如果没有中断,获取下一条指令

如果中断:

暂停当前程序的执行

保存状态

设置 PC 为中断处理程序例程的起始地址

过程中断

恢复状态并继续中断的程序

# 多重中断

- 定义:多个中断同时发生

- 处理多个中断的方法:

- 禁用中断

- 处理器在处理一个中断时将忽略其他中断

- 中断保持挂起状态,并在第一个中断被处理后进行检查

- 中断在发生时按顺序处理

- 定义优先级

- 低优先级的中断可以被高优先级的中断中断

- 当更高优先级的中断被处理后,处理器返回到前一个中断

- 禁用中断

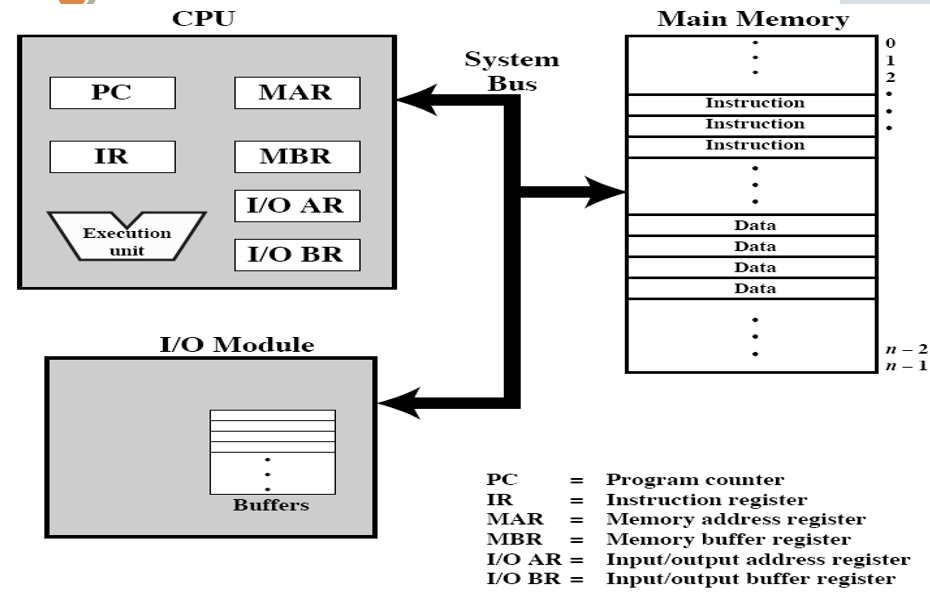

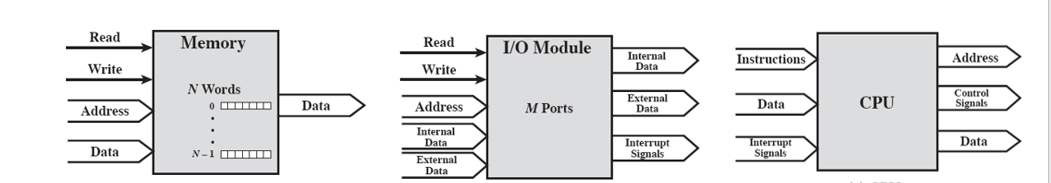

# 互联结构

- I / O 功能

直接与处理器交换数据

在某些情况下,直接与内存交换数据

直接内存访问 (DMA) - 第 7 章

- 转发类型:

存储器到处理器

处理器到内存

I/O 到处理器

处理器到 I/O

I/O to or from 内存 - DMA

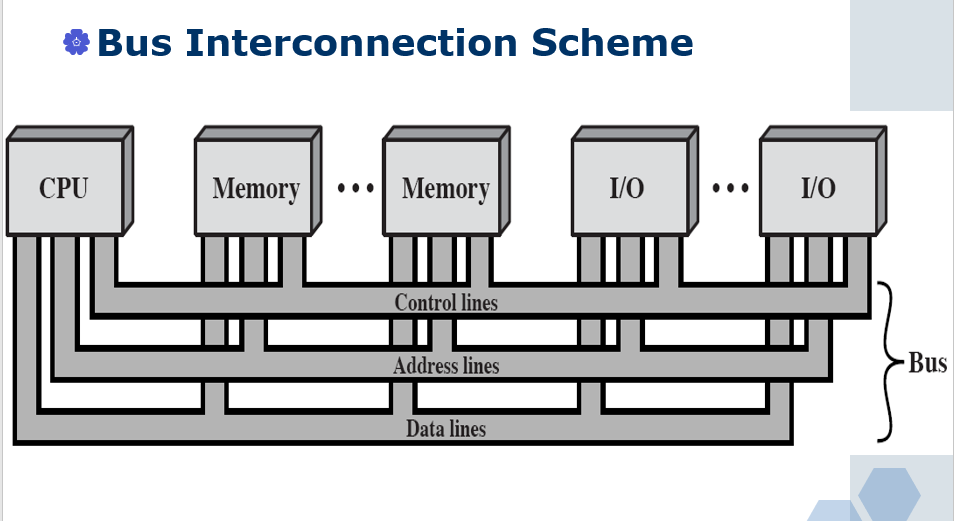

# 总线互联

- 定义:连接两个或多个组件的通信路径

- often grouped

在一个总线上的若干通道,例如 32 位数据总线是 32 个单独的单位通道 - 总线宽度:线路的数量

- 总线的主要特点:提供共享的传输介质

- 总线类型:系统总线、外围总线、内部总线

- 系统总线:连接计算机主要部件的总线

- 数据总线,地址总线,控制总线

- 系统总线:连接计算机主要部件的总线

# 数据总线

- 功能:进位数据

请记住,在这个层次上,“数据” 和 “指令” 没有区别

每一行一次只能携带 1 位 - 数据总线宽度是决定系统性能的一个关键因素

8、16、32、64 位 - 机器字长:机器在整数运算中可以处理的最多二进制位

数据总线宽度 = 机器字长

= 主寄存器长度

# 地址总线

- 功能:标识数据的来源或目标

例如:CPU 需要从内存中给定的位置读取指令 (数据) - 地址总线宽度决定了系统的最大存储容量

例如,8088 有 20 位的地址总线,提供 1M 的地址空间

# 控制总线

- 功能:传递控制信号

控制数据和地址总线的使用 - 控制信号:命令和定时信息

内存读写信号

I / O 读 / 写

传递 ACK

总线请求

总线授权

中断请求 & ACK

时钟信号

重置

# 总线物理结构

总线看起来像什么?

- 电路板上的平行线

- 带状电缆

- 在母板上剥离连接器

如 PCI - 导线组

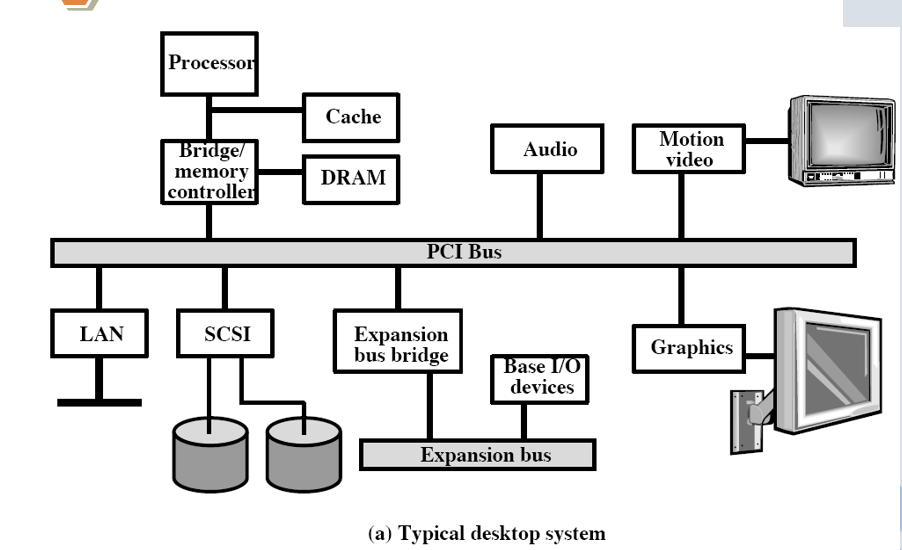

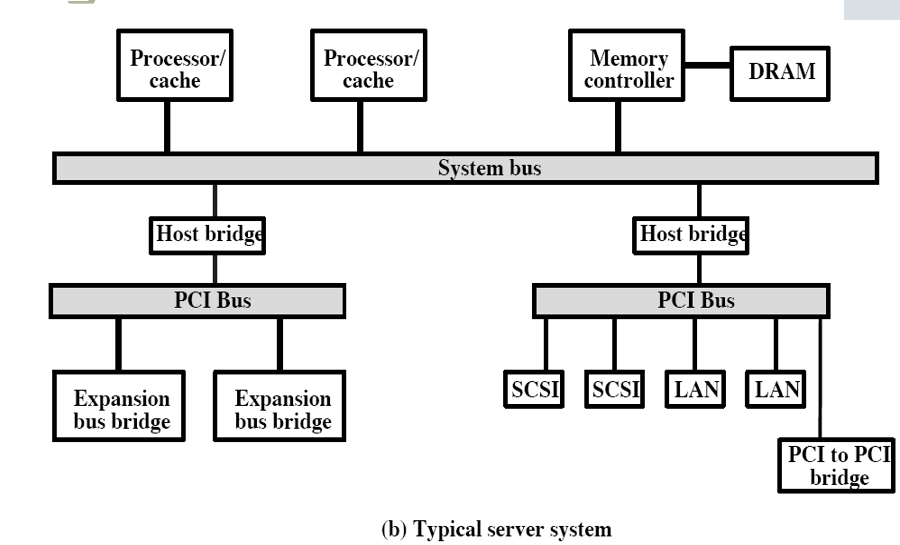

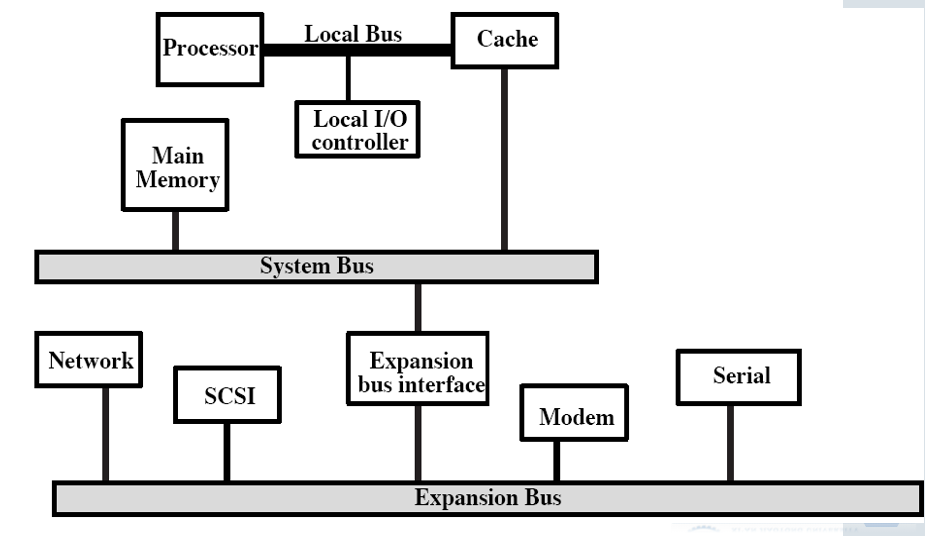

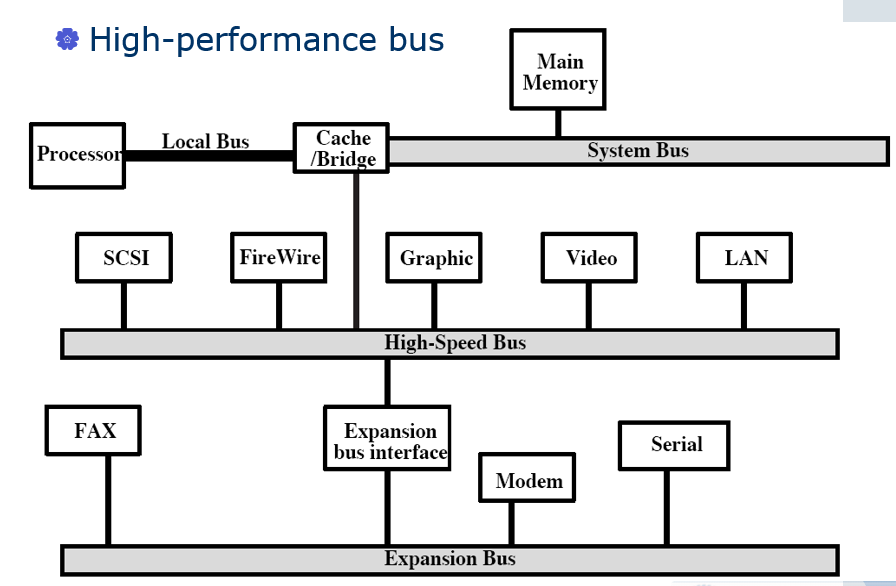

# 多个总线层次结构

- 单总线问题

- 同一总线上的大量设备导致:

- 传播延迟 (瓶颈)

更多的设备意味着更长的总线,这将导致更大的延迟。长数据通路意味着总线使用的协调会对性能产生负面影响

如果聚集数据传输接近总线容量

- 大多数系统使用多个总线来克服这些问题

# 总线设计要素

# 类型

- 多个总线,例如独立的数据和地址线

- 优势:高通量

- 缺点:规模和成本增加

- 多路复用总线:

- 分时复用,共享线路

- 地址有效或数据有效的控制线

- 优点:更少的线路,空间,成本

- 缺点:

- 更复杂的控制

- 最终的性能

# 总线仲裁

- 多个模块使用总线

例如 CPU 和 DMA 控制器 - 一次只能有一个模块控制总线

- 仲裁方法:

- 分布式:没有集中控制器,每个模块包含一个访问控制逻辑

- 集中式:总线控制器 / 仲裁器负责总线的使用和时间。CPU 的独立模块或部分

- 单独的请求

- 优点:快速反应,灵活优先

- 缺点:线路过多,控制复杂

- 链轮询

- 优点:可拓展的

- 缺点:对电路故障敏感

- 计数器定时轮询

- 优点:灵活的优先级,对电路故障不敏感

- 缺点:复杂控制

- 单独的请求

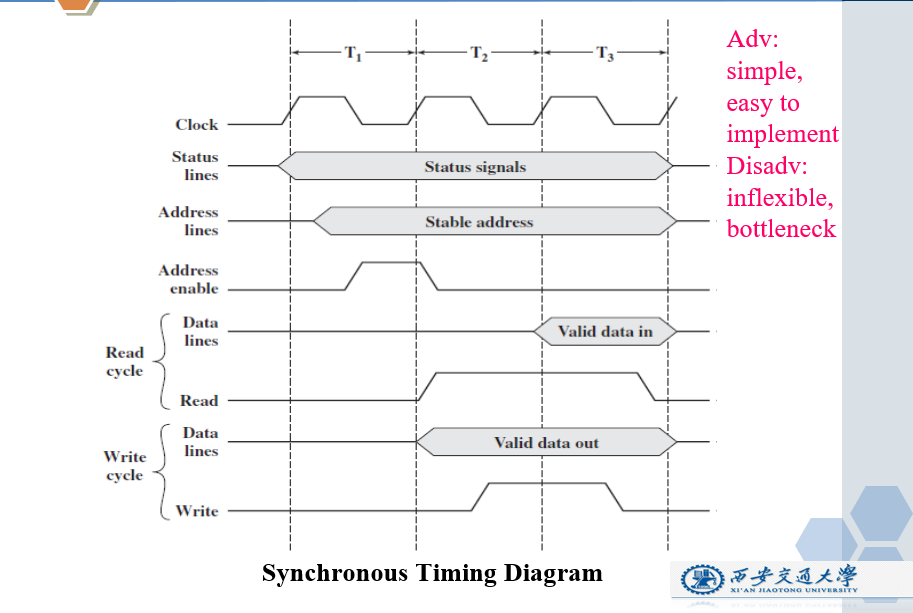

# 时钟

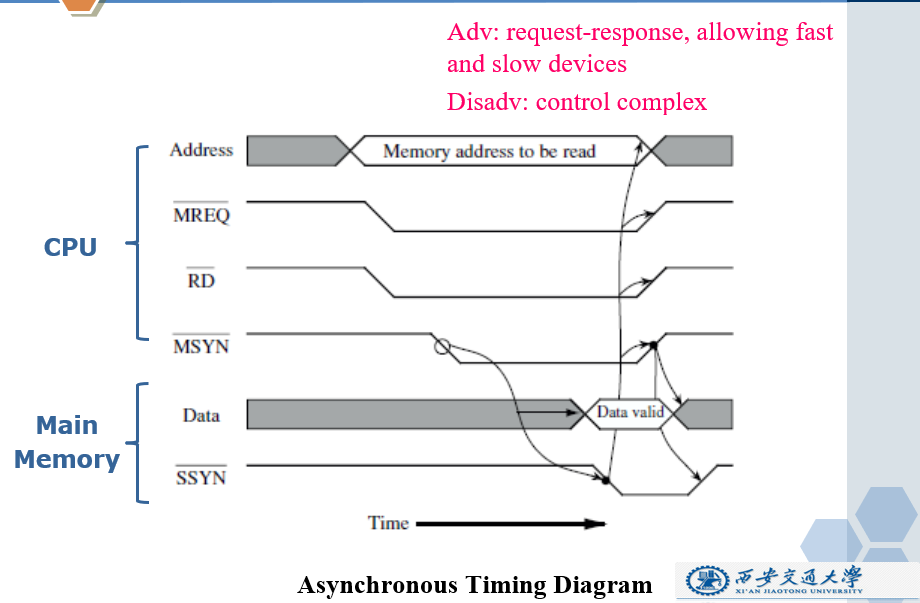

# 总线的通信控制方式

- 通信控制:解决如何开始和结束传输,如何协调主从模块

- 根据时间的不同,通常可以采用四种通信方式

同步

异步

Half-synchronous

分离

# 时钟

- 定义:事件在总线上进行协调的方式

- 同步计时:事件的发生由时钟信号确定

- 控制总线包括时钟线

- 一个单一的 1-0 传输是一个总线周期或总线周期

- 所有设备都可以读取时钟线

- 通常在前缘同步

- 通常是一个事件的单一周期??

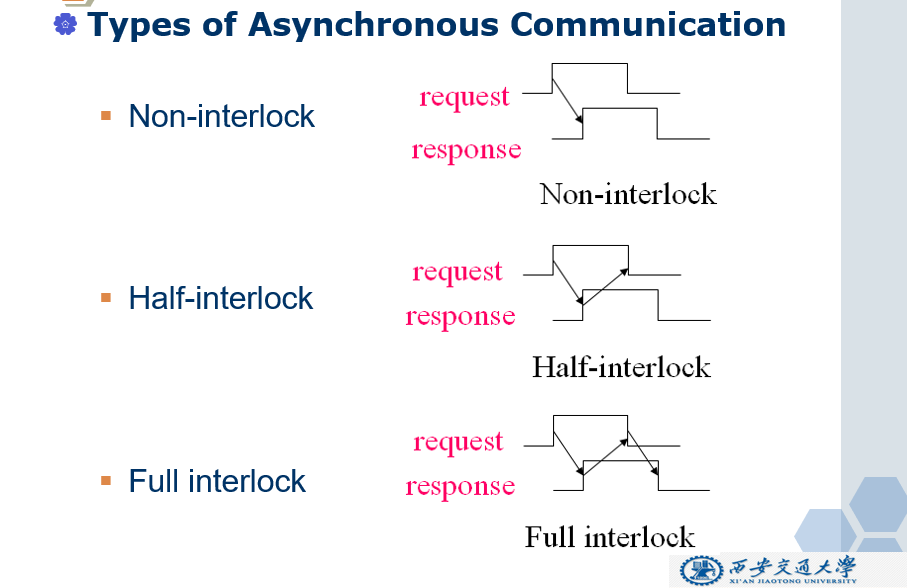

- 异步计时:总线上的一个事件发生在前一个事件之后,并依赖于前一个事件的发生

- Half-synchronous

- 单独的通信

# 同步时序图

# 异步步时序图

异步通信的种类

# Half-synchronous 通信

需要时钟

需要排队等候

允许各种速度模块和谐通信

用于连接低速及较大差速设备

# 单独的通信

- 基本思想是:

将总线周期分成两个子周期

在第一个子周期中,master 将指令、地址等信息放入总线,然后丢弃总线

在第二个子周期,从开始准备数据 (选择,解码,加载),然后应用总线并发送数据 - 优点:避免总线空等待

- 用于大型计算机

# 总线宽度

地址

数据

- 总线宽度 width

数据总线的宽度对系统的性能有很大的影响

地址总线的宽度对系统容量有一定的影响 - 总线带宽 bandwidth

总线的传输速率,b/s

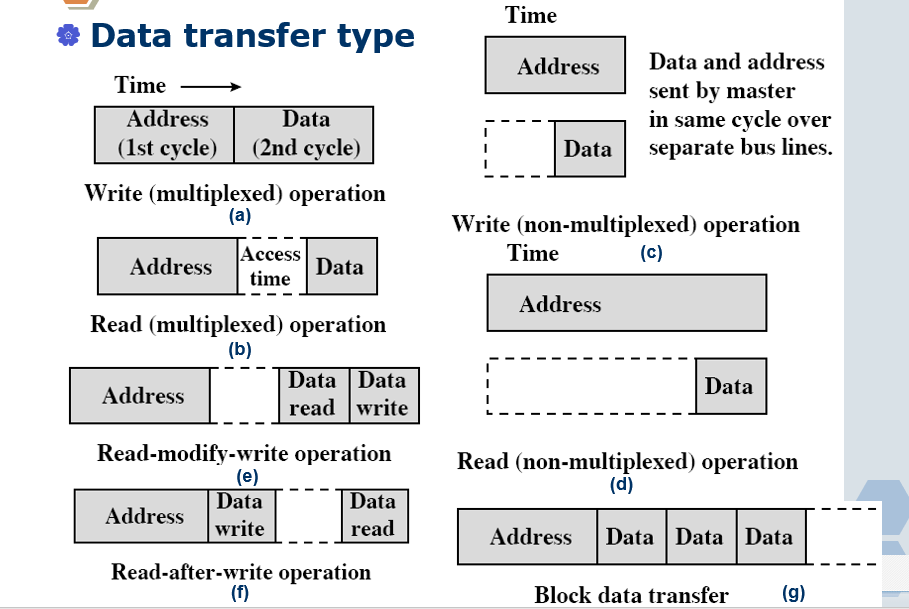

# 数据转发方式

读,写,读修改写,读后写,锁定

# PCI

- PCI (Peripheral Component Interconnection): 又称高速 I/O 总线

英特尔向公众发布 - 不依赖 cpu,高带宽,便宜

- 64 位,264 mbps / 4.2 gbps

- 能与其他总线互连

- 集中控制和同步定时,隐藏仲裁

![图9]()

![图10]()

# Supplement

- ISA (industrial standard architecture)

Intel,16bit, also called AT bus,8MHz,16MB/s

Low performance bus, CPU participant - EISA (extended industrial standard architecture)

ISA Compatible, 32bit

8MHz,33MB/s - VL-BUS:

local bus standard proposed by video electronic standard association

Evolved from CPU bus,33MHz,32bit

High-performance bus used for CPU and high speed devices - USB (Universal Serial Bus)

Flexible

faster

Connector with low cost cable and hub

# 词汇

-

Hardwired program: 硬布线编程

-

Interrupt request: 中断请求

-

Interrupt handler routine: 中断处理程序

-

Multiple interrupts: 多重中断

-

DMA(direct memory access): 直接存储器访问

-

Port:端口

-

Module: 模块

-

Fast Ethernet:快速以太网

-

Packet-switching network:分组交换网

-

LAN:局域网

-

Time(frequency) multiplexing: 时 (频) 分复用

-

Adapter:适配器

-

Arbitration: 仲裁

-

Synchronous (Asynchronous) timing: 同(异)步时序

-

Master (slave) synchronous:主(辅)同步

-

Multiprogramming system:多道程序系统

-

PCI(peripheral component interconnect): 外设互连(总线)

# keypoint

Interrupt and instruction cycles

Multiple interrupts

System bus

Multiple bus hierarchy

Key elements of bus